# Development of Type-2 Hypervisor for MIPS64 Based Systems

December

2015

[10th Deliverable]

This document is version 10 of first report and includes the implementation details of current deliverable of "Development of Type 2 Hypervisor for MIPS64 based Systems" project, funded by National ICT R & D Fund Pakistan. The report starts with brief description of project objectives, technical details of our approach, challenges and their solutions. Complete description of testing infrastructure, test cases and test results are discussed later on. The report concludes with the impact of current deliverable on the overall project progress.

Test Cases Result Report

# TABLE OF CONTENTS

| 1 | Projec       | t Description                       | 1  |

|---|--------------|-------------------------------------|----|

| 2 | High I       | Level Design                        | 2  |

| 3 | Imple        | nentation Strategies                | 3  |

|   | 3.1 I        | nstruction Level Execution Model    | 3  |

|   | 3.2 I        | Block Level Execution Model         | 4  |

| 4 | Systen       | 1 Development                       | 5  |

|   | 4.1 M        | Memory Management Unit (MMU)        | 5  |

|   | 4.1.1        | GVA to GPA Translation              | 7  |

|   | 4.1.2        | GPA to HVA Translation              | 7  |

|   | 4.1.3        | Page Table                          | 7  |

|   | 4.1.4        | Translation Look-aside Buffer (TLB) | 8  |

|   | 4.1.5        | Bugs Fixed in TLB                   | 8  |

|   | 4.1.6        | Cavium Segment Implementation       | 9  |

|   | <b>4.2</b> N | MIPS Instruction Set Translation    | 9  |

|   | 4.2.1        | Privileged Instructions             | 10 |

|   | 4.2.2        | Unprivileged Instructions           | 11 |

|   | 4.2.3        | Cavium Specific Instructions        | 13 |

|   | 4.2.4        | Branch and Jump Instructions        | 15 |

|   | 4.2.5        | Control Shifting Instructions       | 18 |

|   | 4.2.6        | Special Instructions                | 19 |

|   | 4.2.7        | Examples of Translation             | 19 |

|   | 4.3          | Software Cache                      | 20 |

|   | 4.3.1        | Cache Storage                       | 21 |

|   | 4.3.2        | Searching a Block                   | 21 |

|   | 4.3.3        | Block Retrieval                     | 21 |

|   | 4.3.4        | Replacement policy                  | 22 |

|   | 4.3.5        | Bugs fixed in Address cache         | 22 |

|   | 4.4          | Fimer Unit                          | 22 |

|   | 4.4.1        | Continuous Tick Timer               | 23 |

|   | 4.4.2        | On-Demand Tick Timer                | 24 |

|   | 45 I         | interrunt and Excention Handling    | 26 |

|   | 4.5.1 | SIGFPE: Floating point exception handling      | 27 |

|---|-------|------------------------------------------------|----|

|   | 4.5.2 | SYSCALL: System call handling                  | 27 |

|   | 4.5.3 | TLB and Address error Exception Handling       | 29 |

|   | 4.5.4 | Modification in Exception Handling             | 29 |

|   | 4.5.5 | External Interrupts                            | 29 |

|   | 4.5.1 | CTRL+C signal for guest                        | 29 |

|   | 4.6   | SMP Support                                    | 30 |

|   | 4.6.1 | Inter-Core Communication Through CIU           | 30 |

|   | 4.7   | IO Device Management                           | 33 |

|   | 4.7.1 | UART                                           | 33 |

|   | 4.7.2 | Central Interrupt Unit (CIU)                   | 36 |

| 5 | Virtu | al Disk                                        | 38 |

|   | 5.1   | Virtio Block Configuration                     | 39 |

|   | 5.2   | Vhost Block Configuration                      | 40 |

|   | 5.3   | Creation of Virtual Disk for Hypervisor        | 41 |

| 6 | Netw  | ork Infrastructure                             | 42 |

|   | 6.1   | Virtio-Net                                     | 43 |

|   | 6.2   | Vhost-Net                                      | 45 |

|   | 6.3   | Network device in hypervisor                   | 46 |

|   | 6.4   | Execution flow of networking                   | 48 |

|   | 6.5   | Test case                                      | 48 |

| 7 | Testi | ng Infrastructure                              | 50 |

|   | 7.1   | Test cases                                     | 50 |

|   | 7.1.1 | Matching System states                         | 50 |

|   | 7.1.2 | Execution Path                                 | 50 |

|   | 7.1.3 | Comparing Console Output                       | 51 |

|   | 7.1.4 | Progress                                       | 51 |

|   | 7.2   | Testing with SMP Support                       | 51 |

|   | 7.3   | Booting with customized minimal initramfs file | 52 |

|   | 7.4   | Virtual Ethernet Card Detection                | 52 |

|   | 7.5   | Assigning a Valid IP to guest                  | 52 |

| 8 | Test  | Results                                        | 55 |

|   | 8.1   | Output of System State Matching Test           | 55 |

|   | 8.2   | Output of Execution Path Test                  | 56 |

|   |       |                                                |    |

| 8.3     | Output of TLB Testing                        |

|---------|----------------------------------------------|

| 8.4     | Output of CIU Testing60                      |

| 8.5     | Output of Hypervisor Console                 |

| 9 Perfo | ormance Optimization                         |

| 9.1     | Performance Tuning                           |

| 9.2     | Previous Performance Improvements            |

| 9.2.1   | Code Structural Enhancement65                |

| 9.2.2   | Hardware Platform66                          |

| 9.3     | Current Performance Optimizations            |

| 9.3.1   | Modification in Cache Replacement polices    |

| 9.3.2   | Modification in Cache Size and Hash Function |

| 9.3.3   | Parallelization of Block translation         |

| 9.3.4   | Reduction in context switching69             |

| 9.3.5   | Block Linking70                              |

| 9.4     | Correctness related bug fixes                |

| 10 E    | valuation Before and After Optimization71    |

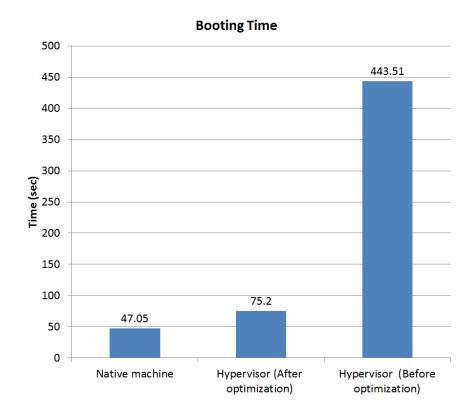

| 10.1    | Booting Time71                               |

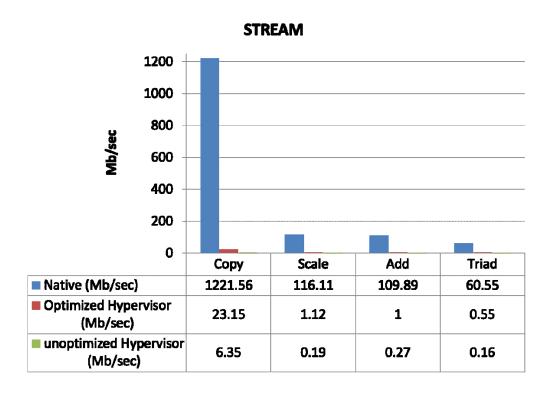

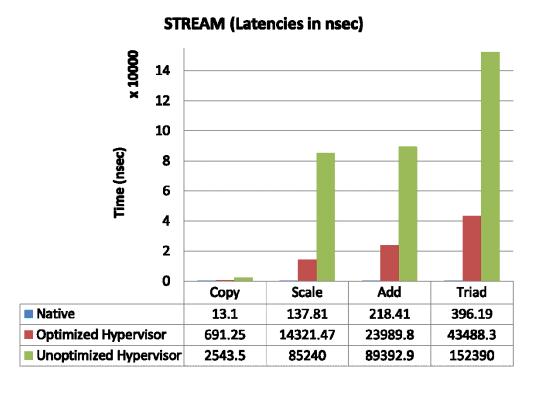

| 10.2    | STREAM72                                     |

| 10.3    | lmbench                                      |

| 10.4    | Linux Testing Project (LTP)                  |

| 11 In   | npact on Project Progress77                  |

# TABLE OF FIGURES

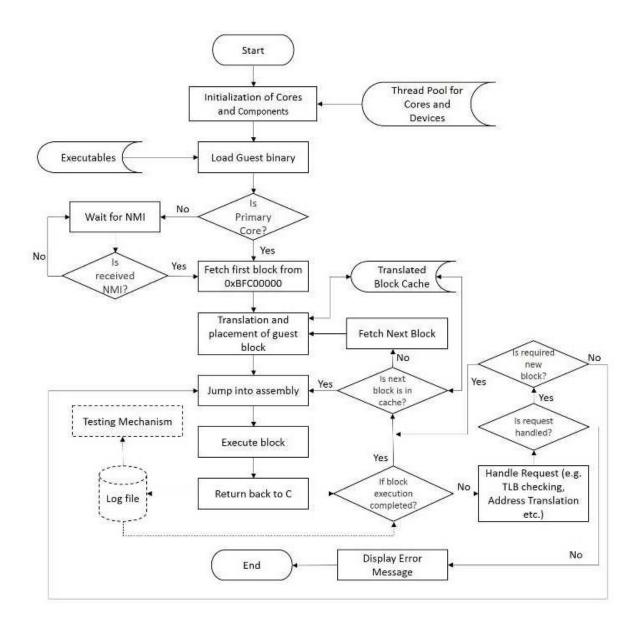

| Figure 1: Multithreaded design of Type-2 hypervisor                        | 2  |

|----------------------------------------------------------------------------|----|

| Figure 2: Instruction level execution model                                | 4  |

| Figure 3: Block level execution model                                      | 6  |

| Figure 4: Code Snapshot of Mtc0's Translation                              | 19 |

| Figure 5: Code Snapshot Of Sll's Translation                               | 20 |

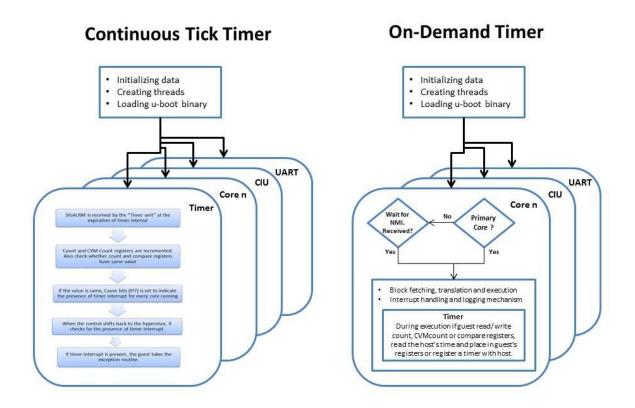

| Figure 6: Continuous Tick Timer Implementation                             | 24 |

| Figure 7: Design Diagram of Two Timer Strategies                           | 25 |

| Figure 8: Exception handling in user mode                                  | 28 |

| Figure 9: Code snippet showing the emulation of exception handling         | 28 |

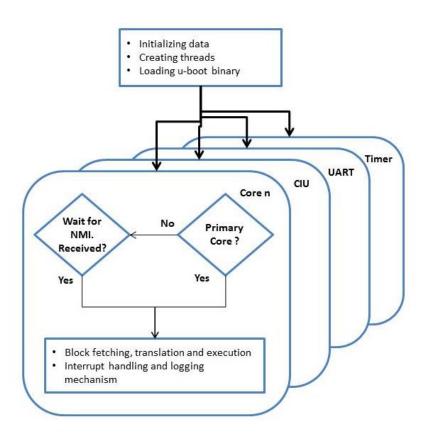

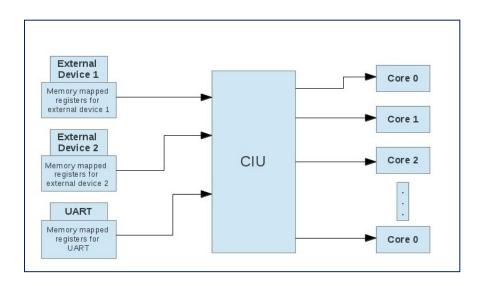

| Figure 10: Multithreaded view of hypervisor and external devices           | 31 |

| Figure 11: Execution flow of hypervisor with SMP                           | 32 |

| Figure 12(a): (ciu) Interrupt distribution from external devices to core   | 37 |

| Figure 13: Memory mapping between core and external devices                | 38 |

| Figure 14: Code Snippet from virtio_blk.c file                             | 39 |

| Figure 15: Commands for Device Creation                                    | 40 |

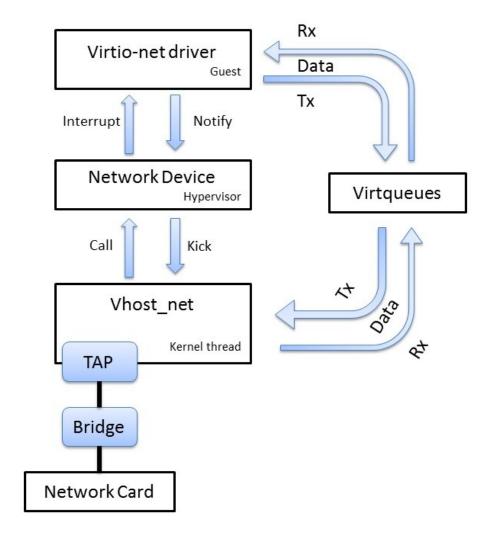

| Figure 16: Networking Infrastructure of Type-II Hypervisor                 | 43 |

| Figure 17: Code Snippet Used for Registering Network Device as MMIO Device | 45 |

| Figure 18: Communication between Virtio-Net, Vhost-Net and Network Device  | 47 |

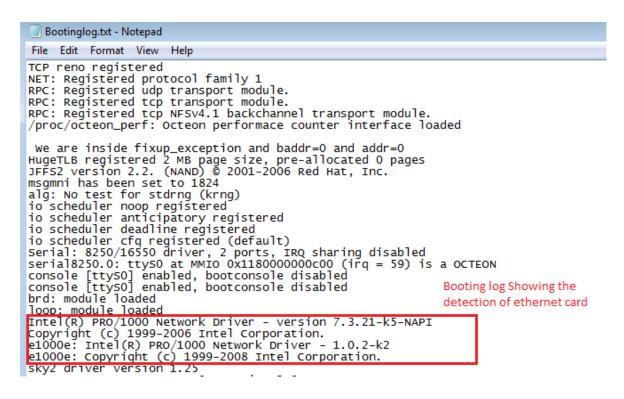

| Figure 19: Active Network Device in Guest                                  | 49 |

| Figure 20: Booting Log of Hypervisor, Showing the Detection of Ethernet    | 53 |

| Figure 21: Guest's Network Interfaces                                      | 54 |

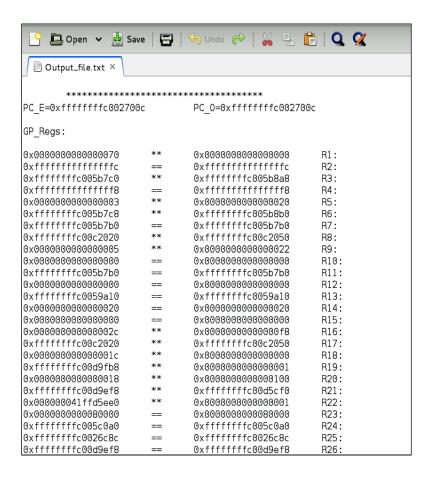

| Figure 22: Output of system state matching test                            | 55 |

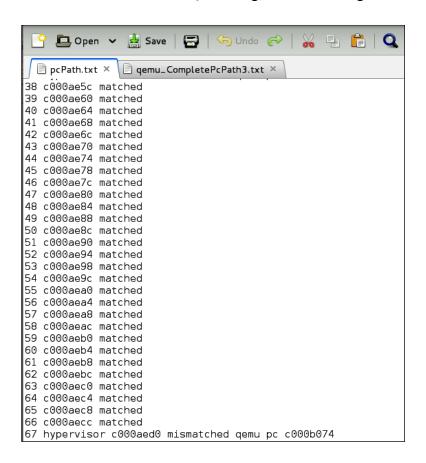

| Figure 23: Output of execution path test                                   | 56 |

| Figure 24: Searching for random TLB                                        | 57 |

| Figure 25: TLB entries in TLB table                                        | 58 |

| Figure 26: Output of TLB and page table testing.                           | 59 |

| Figure 27: Output of CIU. No pending interrupt on core 1                   | 60 |

| Figure 28: Output of CIU. No pending interrupt on core 0                   | 61 |

| Figure 29: Booting log of hypervisor                                       | 62 |

| Figure 30: Comparison of Booting Time                                      | 72 |

| Figure 31: Transfer Rate for Stream Operations                             | 73 |

| Figure 32: Latencies for Stream Operations                                 | 73 |

| Table 1: Sorted Flat Profile Before Optimization (Showing More Time Consuming Functions Only) | 63 |

|-----------------------------------------------------------------------------------------------|----|

| Table 2: Sorted Flat Profile after Software Cache Implementation                              | 64 |

| Table 3: Sorted Flat Profile After In-Place Block Execution Implementation                    | 65 |

| Table 4: Specification of Old Evaluation Board                                                | 67 |

| Table 5: Specification of New Evaluation Board                                                | 67 |

| Table 6: Lmbench Output for Different Memory Operations                                       | 74 |

| Table 7: Lmbench Bandwidth Results for File Mmap                                              | 75 |

| Table 8: Lmbench Latency Results for File Mmap                                                | 75 |

| Table 9: Lmbench Bandwidth Results for File Reading                                           | 75 |

| Table 10: Lmbench Latency Results for File Reading                                            | 76 |

| Table 11: Lmbench Bandwidth Results for Pipe And Unix                                         | 76 |

| Table 12: Lmbench Results of Network Through-Put                                              | 76 |

|                                                                                               |    |

# 1 PROJECT DESCRIPTION

The main objective of this project is to develop an open source Type-2 hypervisor, for Linux-based MIPS64 embedded devices. Type-2 means that it is a hosted hypervisor which runs on MIPS64 based Linux systems as a Linux process. It is intended that the hypervisor will (1) support installation and execution of un-modified MIPS64 Linux guest(s) on un-modified MIPS64 Linux host (2) take advantage of virtualization for improved hardware utilization and performance optimization, by using multiple MIPS cores. Our focus on MIPS is due to the fact that MIPS based systems are lagging behind in the use of virtualization. One of the reasons is that many MIPS based processors are used in low end consumer devices like TV set top box, GPS navigation system and printers. There isn't a clear cut use case for virtualization here. But few of the MIPS vendors target higher end embedded devices like network switches and routers, GSM/LTE base station equipment and MIPS based blade servers. There are clear-cut virtualization use cases for this higher-end MIPS segment.

The development started on April 1, 2013 and first deliverable was due after 3.5 months i.e. July 15, 2013. In first deliverable, we built the required infrastructure. The infrastructure printed guest kernel banner on console at the end of 1st deliverable. Second deliverable was due after 6.5 months of commencement data i.e. October 15, 2013. The milestone in 2nd deliverable was the dynamic code patching of one sensitive guest instruction with one safer instruction. In 3rd deliverable, dynamic code patching was augmented by implementing cases where one sensitive instruction is replaced by more than one instruction. In 4th deliverable, dynamic code patching was applied on demand. In 5th deliverable, guest kernel booting completes and starts creating user mode processes. In 6th deliverable, SMP support was added to whole infrastructure and many performance related bugs were fixed. In 7<sup>th</sup> deliverable major units like Timer and UART were added, in code. Exception and interrupt handling mechanism was further developed. Bugs related to memory implementation and instruction execution were fixed. In 8<sup>th</sup> deliverable, virtual disk implementation was added to the infrastructure. Also Ethernet card detection inside the guest has been done. There were some bug fixes related to timer, TLB and exception handling mechanism. In 9<sup>th</sup> deliverable, a valid IP was assigned to the guest. Timer infrastructure was changed due to bad performance. Many TLB and UART related bugs were fixed. An error in block fetching mechanism was identified and corrected. Some code structural changes were

done for improving timing performance of hypervisor. Ctrl+C implementation was provided by hypervisor for killing guest processes. In 10<sup>th</sup> deliverable, a complete network infrastructure is implemented. In the next three month extension time period, optimization has been in focus. Numbers of strategies were implemented to achieve better time performance.

# 2 HIGH LEVEL DESIGN

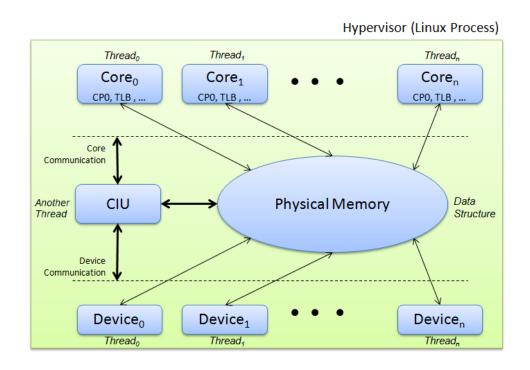

Type-2 hypervisor behaves like an ordinary Linux process that could be scheduled by host operating system. However, this process has to present a holistic view of virtual hardware for guest operating system(s) to run on it. Virtual hardware consists of software representations of CPU cores, memory and peripheral devices. In real hardware, CPU cores and devices work concurrently and could be considered as processes or threads in software representation. Multiprocessing requires inter-process communication (IPC) whereas multithreading could be implemented using the shared address space. Each one has its own pros and cons. We selected multithreaded design for our hypervisor, as shown in Figure 1. It shows that each core and device is a separate thread. Central interrupt unit (CIU) is another thread that dispatches pending interrupts to the cores using mapped memory.

FIGURE 1: Multithreaded design of Type-2 hypervisor

# 3 IMPLEMENTATION STRATEGIES

Primarily, we have experimentally implemented two different strategies to develop Type-II hypervisor. Firstly, we implemented an instruction level strategy. This strategy is very simple and easier to implement but it greatly reduces time efficiency in order to boot a guest OS because we take trap and then emulate every instruction of the guest OS. It also demands a lot of programming effort because we have to provide almost all MIPS ISA functionality implementation in our hypervisor code. Secondly, on the other hand, we also implemented a block level technique for the execution of guest OS. Because in this strategy, we fetch and translate a set of instructions at a time instead of a single instruction emulation that's why it can be considered a better and faster approach form the previous strategy. We discussed both implementations as follows.

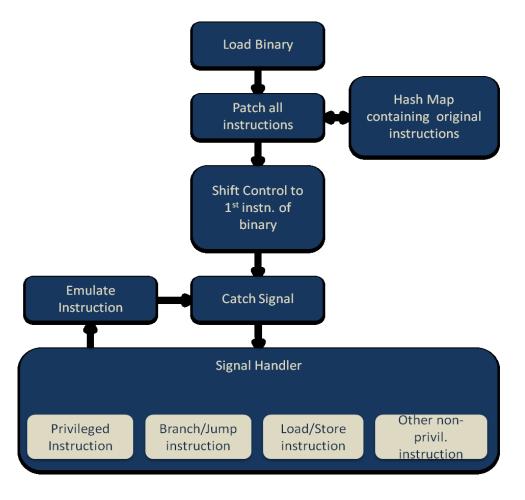

# 3.1 Instruction Level Execution Model

It is a very simple mechanism to execute a Guest executable binary on the hypervisor. In this strategy, when executable guest OS is loaded then we patch all instructions of the guest OS binary with a trap-call instruction and original instructions are placed into a lookup table (hash-table). Patching means an instruction is replaced with another instruction, which is caused to generate a trap during its execution. By doing so, when the control is shifted on the guest application binary for its execution then we get a signal from the hardware on each instruction because of its patching. This signal is catch by the signalHandler into the hypervisor code, a method which is able to catch signal generated by the hardware. Now the control comes back to our hypervisor code and we can emulate the corresponding instruction into our software based environment also called a virtual environment. In software based environment, we actually have a complete soft image of MIPS's processor.

We have all GP (General Purpose) registers, CP0 registers, TLB, CIU and exception handling mechanism in our software based environment, which is provided by the hypervisor to the guest operating systems for their execution.

FIGURE 2: Instruction level execution model

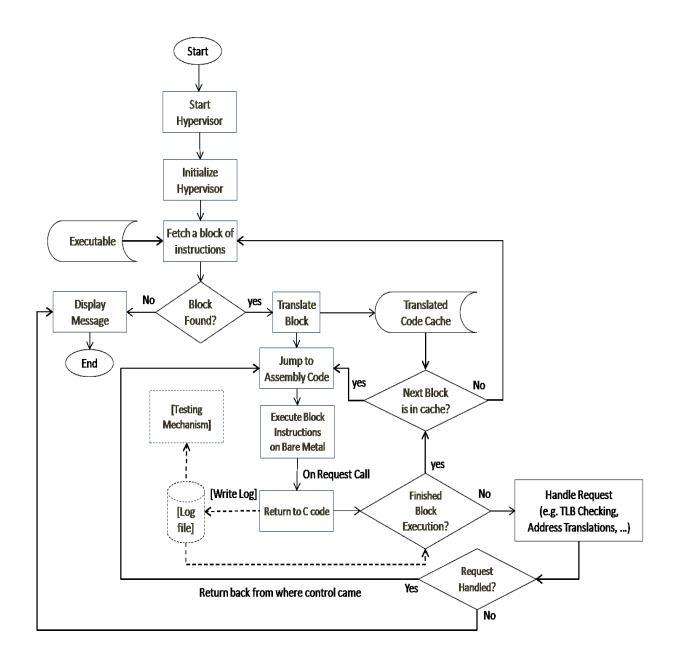

# 3.2 BLOCK LEVEL EXECUTION MODEL

This strategy is very much different from the above mentioned strategy because it provides block level instruction emulation instead of instruction level trap & emulation mechanism. A block consists of a set of instructions having only one jump/branch instruction as a second last instruction. In this strategy, we actually fetch a block from a corresponding PC address of the guest OS loaded binary and then translate this block. Each instruction in the block fetched from Guest binary is translated into a number of instructions, which are executable on the host machine. The translated instructions are composed in the same order as the original instructions are given in the Guest binary block to preserve the correct behavior of instructions. The translated block is then placed into a Cache-blocks for future reusing purpose so that if the same block is required again then no need to fetch again and retranslate that block if it's available in

the Cache-blocks. After block translation we execute it by just placing the starting address of this block into PC register so that this block can be executed.

During execution a block, the control may come into hypervisor code in case of address translation from guest virtual address to host virtual address or any other interrupts or for log files writing purpose. The first block in fetched from the guest virtual reset vector 0xBFC00000 address and then it is translated and after its translation, it is placed into some fixed location memory where control is then shifted at that memory location for the execution of translated block. When whole the execution of translated block is completed, the control comes back into the hypervisor code for fetching the next block. Now, we first check whether the new required block is available into Cache-blocks or not. If it is found in the Cache-blocks then it doesn't need to fetch again and retranslate the required block because the Cache-blocks already have this translated block into it. The control is just placed on the new block, which has been found into the Cache-blocks. Alternatively, if required new block doesn't found into the Cache-blocks then it is fetched, translated and also cached into the Cache-blocks. The Cache-blocks may contain some fixed number of translated blocks into it when it becomes full then one block from it, is replaced by new translated block based on some replacement policy. Figure 3 shows the flow chart of block level execution model of hypervisor.

# 4 SYSTEM DEVELOPMENT

The whole infrastructure of the hypervisor is divided into modules. The implementation functional description of each unit is given detail below.

# 4.1 MEMORY MANAGEMENT UNIT (MMU)

It is the most important unit of a computer system. The purpose of memory management unit is to translate virtual addresses to physical addresses. For virtual address translation, some rules are already defined by physical hardware and we implemented these rules in software to provide the virtualization of MMU used by guest operating system(s). In case of hypervisor, it is used to translate GVA to HVA. To translate GVA to GPA, we use same method as used by the hardware. For translation of GPA to HVA, we use hash map to store information of all regions mapped in host virtual address space.

FIGURE 3: Block level execution model

## 4.1.1 GVA TO GPA TRANSLATION

MIPS64 architecture supports both 32-bit and 64-bit Addressing modes. In 32-bit addressing mode, address segment is defined by upper 3 bits (i.e. bits 32-29) of virtual address. If these bits are 100 then it is kseg0 region. It is directly mapped to physical memory. If these bits are 101, address is from kseg1 region and this is also directly mapped to physical memory. In both previous cases, lower 20 bits represent physical address. For 110, region is ksseg. This is not directly mapped and we have to search for it in TLB for address translation. For 111, region is kseg3 which is not directly mapped and we have to search TLB for valid entry to translate the address. If these bits are 0xx then it is useg. Translation for useg is slightly different. If ERL bit of status register of CP0 is set then useg is directly mapped to physical memory. If ERL bit is not set then we have to check TLB to get physical address.

In 64-bit addressing mode, address segment is defined by upper 2 bits (i.e. bits 63-62) of virtual address. If these bits are 10, then this is xkphys region which is directly mapped to physical memory or I/O devices. If 49th bit of virtual address is 0 then it is memory access and lower 29 bits represent physical address of memory. If 49th bit is 1 then it is I/O address and data is load/store from respective device. If these bits are 11 then it is xkseg region which isn't directly mapped and we have to search TLB for valid address translation. For 01, region is xsseg which is also to be searched in TLB for translation. For 00, region is xuseg. If ERL bit of status register of CPO is set then it is directly mapped otherwise TLB translation would be required.

# **4.1.2 GPA TO HVA TRANSLATION**

All physical memory regions of a machine are mapped in virtual address space of hypervisor. Once we get the valid translation for GVA, we have to translate that physical address to HVA in order to access valid data. After getting valid physical address, we found the memory region or I/O device to which it belongs. We simply find HVA for required memory region or I/O device using hashmap. Once we get a valid GVA-to-HVA translation, we can simply execute the respective instruction.

# 4.1.3 PAGE TABLE

In MIPS no physical page table is provided by hardware and page table is solely managed by operating system. Hence, there is no need to implement page table.

# 4.1.4 TRANSLATION LOOK-ASIDE BUFFER (TLB)

TLB is a cache used to speedup virtual address to physical address translation. In case of type 2 hypervisor, TLB translates GVA to HVA. There are four basic TLB functions: probe, read, write-random and write-index. TLB probe searches for a TLB entry using the value of EntryHi register of co-processor 0 (CP0). If valid entry is found, it places index of TLB entry in CP0 index register, otherwise it sets probe bit of index register and consult page table. TLB read gets value from CP0 index register and checks the validity of data at this index. If data is valid, the components of entry (i.e. entryHi, entryLo0, entryLo1 and page-mask) are moved to corresponding CP0 registers. Otherwise TLB read raises invalid data exception. TLB write-random gets index of TLB entry from CP0 random register and checks the validity of data at the index. If entry is dirty, it raises dirty data exception, otherwise it writes corresponding values of CP0 registers (i.e. entryHi, entryLo0, entryLo1 and page-mask) to the TLB entry at that index. TLB write-index works same as TLB write-random except that it gets index value from CP0 Index register.

On TLB miss or TLB Mod exception, we jump to the exception handler entry point from where the kernel determines which kind of exception it is and service the exception.

# 4.1.5 BUGS FIXED IN TLB

- TLB Restructuring: TLB structure and searching mechanism is modified to accommodate changes related to core mask. At boot time when control passes from uboot to Linux kernel, core mask is changed which caused TLB exception in previous implementation and kernel crashes but on such thing happens on actual hardware. Some debugging revealed that searching mechanism on hypervisor is slightly different from hardware. In order to search TLB entry, hardware uses pagemask of each entry placed in TLB instead of using pagemask value of CP0 register.

- Reserved Bits for TLB Registers: Some bits for EntryHi, EntryLo and Pagemask registers are reserved and shouldn't be changed by the guest operating system. Changing these bits can cause problem in translation of virtual address and sometimes cause kernel crash. Masking of such reserved bits was provided for correct virtual address translation mechanism

#### 4.1.6 CAVIUM SEGMENT IMPLEMENTATION

CVMSEG LM is a segment that access portion of DCache as local memory. Larger the size of this segment, smaller the size of DCache. CVMSEG IO has only one legal address 0xFFFFFFFFFFA200 and store to this address issues IOBDMA command which returns data from IO bus to CVMSEG.

Operating system normally uses this region as scratch pad memory and register values are stored at these locations during context switching. Implementation of this region was crucial for successful booting.

# 4.2 MIPS Instruction Set Translation

MIPS instructions are mainly categorized as R, I and J types. "R" category contains those instructions which use on gp registers. I types involves an immediate value plus register and J type has target address field, no registers to manipulate.

The idea is to not completely emulate the instruction but rather change the registers embedded in instruction and execute it on hardware as it is. The registers that are replaced are first loaded with the expected contents. These loading instructions are also written in assembly language. The complete translation of an instruction will have some loading instructions then the actual reconstructed instruction and then some storing instructions. Control shifting and flow control instructions are treated differently.

We have a memory based copy of all registers (i.e. GP, CP and special registers) which belongs to guest OS. After the execution of particular instruction, guest's registers would also be updated accordingly. For translating mips instructions into equivalent set of instructions which

will produce same results in the registers kept for guest, we use 3 gp registers. The expected contents (from host's point of view) of the registers are first loaded in these registers and then replaced in instruction to be executed. Results are then saved to our memory based registers.

The categories are based on the type of instruction, privileged or unprivileged, how many registers are used, what is destination register and how the fields are manipulated.

Below are the categories and the instructions included in them are also mentioned.

# **4.2.1 Privileged Instructions**

Instructions which involve Co-processor 0 registers are privileged instructions and can't be executed in user mode. Privileged Instructions are treated separately.

- **mfc0**: The translated set of instructions will load the contents from particular cp register and store in the place of destination gp register in the memory.

- mtc0: The translated set of instructions will load the contents from particular gp register and store in the place of destination cp register in the memory. It also checks whether destination register is \$0 or not. If it is then the instruction is replaced with "nop". Certain bits of cp registers are reserved. To avoid over writing them, masking is used.

- **tlbr/ tlbwi/ tlbwr/ tlbp**: In case of tlb instructions, an integer is placed on a particular place in the memory and control is shifted back to handlerRequest(). The control mark indicates the instruction to be handled accordingly.

- **di** (disable interrupts): First the contents of status register is loaded. If any destination register is given then the contents of status register is stored at destination register. First bit of status register is cleared to disable interrupts and the contents are stored in the status register.

- **ei** (enable interrupts): First the contents of status register is loaded. If any destination register is mentioned then the contents of status register is stored at destination register. First bit of status register is set to enable interrupts and the contents are stored in the status register.

- **eret** (exception return): when exception routine end, eret is executed to return to the pc from where we have received exception. In its implementation we first check whether erl bit of status register is set or not. If set then error epc is returned, if not then epc value is returned. The returned value is assigned as next pc to be executed.

#### 4.2.2 Unprivileged Instructions

Unprivileged Instructions are grouped on the basis of their type and functionality.

# unprev R

- All those R-type unprivileged instructions, which use 3 gp registers. 2 source gp register and one destination gp register.

- Includes: baddu, dmul, dpop, pop, or, sllv, dsllv, srlv, dsrlv, rotrv, drotrv, srav, dsrav, movz, movn, add, dadd, addu, daddu, sub, dsub, subu, dsubu, and, xor, nor, slt, sltu, mul, wsbh, seb, seh, dsbh, dshd, clz, clo, dclz, dclo, seq, sne (40 total)

- First 2 source registers are loaded from memory into register \$12 and \$13. The register in the instruction to be translated is replaced with these registers and executed as it is. The result is stored on the destination memory based gp register.

# • shift R

- All those R-type unprivileged instructions, which are shift instruction and the no. of times to be shifted is encoded in instruction itself (i.e field from bit 6 to 10). 1 source gp register and 1 destination gp register.

- Includes: dsrl, srl, dsll, sll, drotr, rotr, dsra, sra, drotr32, dsll32, dsrl32, dsra32 (12 total)

- First source register is loaded from memory into register 12. The register in the instruction to be translated is replaced with the register and executed as it is. The result is stored in the destination memory based gp register.

# mulDiv R

- All those R-type unprivileged instructions, which multiple or divide and the destination registers are special register HI and LO (opposite to mul instruction included in uprev\_R, whose destination is also a gp register) and 2 source gp registers.

- Includes: dmult, mult, dmult, multu, ddiv, div, ddivu, divu, madd, maddu, msub, msubu (total 12)

- First source registers are loaded from memory into registers 12 and 13. The instruction to be translated is replaced with these registers. After the execution of

these instructions the result will be in HI and LO special registers. Mflo and mfhi is executed after these instructions. The result is stored in the guest's Hi and LO.

For instruction "madd", HI and LO are registers of the hardware is also updated first before executing it.

# moveFromLoHi R

- For moving contents from HI and LO special registers into the gp registers, contents

are loaded from HI and LO and saved at the place of destination gp register.

- Includes: mflo, mfhi (total 2)

# • moveToLoHi R

- For moving contents to HI and LO special registers from gp registers, contents are loaded from particular gp register and saved at the place Hi or Lo register.

- Includes: mtlo, mthi (total 2)

# • ext R (extract)

- These are R-type instructions, whose fields are used differently than the previous categories. Bit 16-20 are used for destination register and bits 11-15 are used for size.

1 gp source and 1 gp destination register is used.

- Includes: ext, dextm, dextu, dext, exts, exts32, (total 6)

- Source register is first loaded in register 12. Then instruction to be translated in executed with 12 and 13 registers. The result in 13 register is stored in the destination gp register.

# • ins R (insert)

- These are R-type instructions, whose fields are used differently than the previous categories. Bit 16-20 are used for destination register and bits 11-15 are used for size. 1 gp source and 1 gp destination register is used. Similar to extract but the difference is that destination register is also loaded before the execution of instruction.

- Includes: ins, dinsm, dins, dinsu, cins, cins32 (total 6)

- Source and destination registers are loaded in register 12 and 13 respectively. Then instruction to be translated in executed with 12 and 13 registers. The result in 13 register is stored in the destination gp register.

# • unprev\_I

- All those I type instructions which use 1 source and 1 destination register (except lui which have no source register but the translation would not produce any error if translated in this category).

- o Includes: daddi, daddiu, addiu, slti, sltiu, andi, ori, xori, lui, addi, seqi, snei (12 total)

- Source register is loaded. Instruction to be translated is executed with register 12 and the result is saved in the destination register's place.

# unprev I Load

- All I-type load instructions

- o Includes: Idl, Idr, Ib, Ih, Iwl, Iw, Ibu, Ihu, Iwr, Iwu, Il, Ild, Id (total 13)

- First the address from where the contents would be loaded is translated in terms of hypervisor. For that the address which needs to be translated is saved on a particular location and control is given to the handler. The translated address is loaded in the register and then the load instruction is executed. The loaded contents are saved on the destination register.

# • unprev\_I\_Store

- All I-type store instructions

- o Includes: sdl, sdr, sb, sh, swl, sw, sh, swr, sw, sc, scd, sd (total 12)

- First the address from where the contents would be stored is translated. For that the

address which needs to be translated is saved on a particular location and control is

given to the handler. The translated address is loaded in the register and then the store

instruction is executed

- LL and SC: Load-Linked and Store Conditional are two instructions which are used to atomically implement read-modify-write using a special LLBit. Assembly instructions are added to translation for correct implementation.

#### 4.2.3 CAVIUM SPECIFIC INSTRUCTIONS

These instructions don't have the standard R, I or J format. Their format is a bit different along with a little difference in their operation from standard instructions.

#### saa

- This instruction atomically adds a word to a memory location.

- This is similar to a store but this instruction directly accesses a memory location contents and adds least significant 32 bits of gp register and save to same memory location. All this operation is done without any interrupt or execution of any other instruction.

- Other store instructions store the contents of gp register to a particular memory location.

- The difference in translation is due to the different format of the instruction. Other store instruction has an offset field but this instruction doesn't have any offset field.

#### saad

• This instruction is similar to saa but the register's content to be added will be considered 64 bit rather than 32 bit.

# • seqi snei

This instruction checks whether the value of gp register is equal to the 10 bit constant, specified in the instruction. If equal, then destination register is set otherwise cleared. The translation is provided accordingly.

#### • v3mulu

This cavium specific instruction performs 192x64 bit unsigned multiplication. Its execution involves special purpose registers P0, P1, P2, MPL0, MPL1 and MPL2. As hypervisor has its own copy of special purpose registers, so before multiplication we have to move the contents of these registers to hardware and then execute multiplication.

#### mtm0

This instruction is R type (related with v3mulu instruction), which could be categorized in unprev\_R. But it moves the contents of gp register to special purpose register (MPL0).

#### • mtm1

• This instruction is R type (related with v3mulu instruction), which could be

categorized in unprev\_R. But it moves the contents of gp register to special purpose register (MPL1).

## mtm2

This instruction is R type (related with v3mulu instruction), which could be categorized in unprev\_R. But it moves the contents of gp register to special purpose register (MPL2).

# • mtp0

This instruction is R type (related with v3mulu instruction), which could be categorized in unprev\_R. But it moves the contents of gp register to special purpose register (P0).

# mtp1

This instruction is R type (related with v3mulu instruction), which could be categorized in unprev\_R. But it moves the contents of gp register to special purpose register (P1).

# • mtp2

This instruction is R type (related with v3mulu instruction), which could be categorized in unprev\_R. But it moves the contents of gp register to special purpose register (P2).

## 4.2.4 Branch and Jump Instructions

These instructions include all variants of branches and jumps. One of the reasons to categorize them separately is due to the execution of delay slot. In this case, two instructions are translated collectively.

# • bne beq (branch if not equal, branch if equal)

- These are only two branch instructions which use two source registers.

- Includes: bne, beq (total 2)

- First the sources registers are loaded into the temp registers and then the delay slot is executed. Branch's source are first loaded due to the fact that delay slot might change the contents of the registers involved in branch. For correct execution of branch its

source registers are loaded in temporary registers. Then the actual branch is executed but with different offset because the target address needs translation. If the branch is taken than offset is added in branch's pc and if not 1 is added in the branch's pc, then this address is stored on a particular place and the control is shifted to the handler.

#### Branch

- Those branch instructions which use one source register.

- Includes: bltz, blez, bgez, bgtz, bltzal, bgezal, bbit0, bbit032, bbit1, bbit132 (total 10)

- First the source register is loaded and then the delay slot is executed. Branch's source are first loaded due to the fact that delay slot might change the contents of the register involved in branch. Then the branch is executed but with different offset because the target address needs translation. If the branch is taken than offset is added in branch's pc and if not 1 is added in the branch's pc, then this address is stored on a particular place and the control is shifted to the handler.

# bne beq likely

- Both instructions use two registers but different from the previous bne\_beq category

due to the fact that the execution of delay slot is conditional. If the branch is taken

then the delay slot is executed otherwise not.

- Includes: begl, bnel (total 2)

- First the sources registers are loaded into the temp registers and the actual branch is executed but with different offset because the target address needs translation. If the branch is taken than delay slot is executed and offset is added in branch's pc and if not 1 is added in the branch's pc, then this address is stored on a particular place and the control is shifted to the handler.

# • branch likely

- These instructions use one register but different from the previous branch category due to the fact that the execution of delay slot is conditional. If the branch is taken then the delay slot is executed otherwise not.

- Includes: bltzl, blezl, bgezl, bgtzl, bltzall, bgezall (total 6)

- First the source register is loaded into the temp register and the actual branch is

executed but with different offset because the target address needs translation. If the branch is taken than delay slot is executed and offset is added in branch's pc and if not 1 is added in the branch's pc, then this address is stored on a particular place and the control is shifted to the handler.

# • **j (jump)**

- It doesn't use any source register. It is an "I" type Instruction.

- Includes: j (total 1)

- First the delay slot is executed then for executing j the target address needs translation. The address is extracted from instruction encoding and placed at a particular place. Then control is shifted to handler.

# • jr (jump register)

- This instruction uses one source register. It is an R type Instruction.

- Includes: jr (total 1)

- First the delay slot is executed then for executing jr the target address needs translation. The address is already in the register, it is placed at a particular location in memory. Then control is shifted to handler.

# • jal (jump and link)

- It doesn't use any source register. It is an "I" type Instruction and differs from previous "j" due to additional linking operation.

- Includes: jal (total 1)

- First the delay slot is executed then for executing jal the target address needs translation. The address is extracted from instruction encoding and placed at a particular place. Then the linking address (i.e. pc+8) is stored in register 31 and control is shifted to handler.

# • jalr (jump and link register)

- This instruction uses one source register. It is an R type Instruction and differs from previous "jr" due to additional linking operation.

- Includes: jalr (total 1)

- First the delay slot is executed then for executing jalr the target address needs

translation. The address is already in the register, it is placed at a particular location in memory. Then the linking address (i.e. pc+8) is stored in register 31 and control is shifted to handler.

#### 4.2.5 CONTROL SHIFTING INSTRUCTIONS

These instructions break the normal execution path and shift the control to exception handler. Executing these instructions as it is on hardware will shift the control to host's exception handler and not of the guest's. During translation, this type of instruction is replaced with the instructions, which will shift control to the hypervisor along with a control mark. Hypervisor will perform exception handling accordingly to control mark value.

• **Trap Instructions:** Trap instructions in a system shift the control to exception handler if the condition is true. This instruction can't be executed as it is on the hardware because if true then the control will shift to host's exception handler. So, the condition is checked before and if true then the control is shifted to handler, otherwise next instruction.

# • teq tne R

- R type trap instructions, which use two source registers.

- Includes: teq, tne (total 2)

- First the condition is evaluated, if true the control is shifted back to hypervisor otherwise next instruction is executed.

# • tge tgeu tlt tltu R

- R type trap instructions, which use two source registers but differs in translation.

- Includes: tge, tgeu, tlt, tltu (total 4)

# teqi\_tnei\_I

- I type instruction, with one source register and 1 immediate value.

- Includes: teqi, tnei (total 2)

## • tgei tgeiu tlti tltiu I

I type instruction, with one source register and 1 immediate value but differ in translation.

- Includes: tgei, tgeiu, tlti, tltin (total 4)

- **Syscall:** In place of syscall, the control is transferred back to the hypervisor with a specific control mark. Hypervisor service the exception accordingly.

- **Break:** In place of break, the control is transferred back to the hypervisor with a specific control mark. Hypervisor service the exception accordingly.

# 4.2.6 SPECIAL INSTRUCTIONS

- **rdhwr:** This is a special instruction which allows reading of some hardware registers while in user mode. Due to current translation, only zero is read into the destination register when this instruction is executed. In case of SMP, it is used to get core number.

- **Pref, deret, cache and ssnop:** These instructions are replaced with "nop".

- Wait: IP (interrupt pending) bits of "cause" register are monitored continuously. If anyone of them is set, indicating the presence of external interrupt, control is shifted back to hypervisor for interrupt handling.

## 4.2.7 EXAMPLES OF TRANSLATION

#### 1. mtc0

If we have an instruction: mtc0 v0, c0\_status. After executing mtc0(), translated instructions would be:

- 1. ld t0, offset(a7)

- 2. sd t0, offset(a7)

```

p void Translation_IPE::mfc0(IInfo * Insp, std::vector<uint32_t, TransInsAllocator<uint32_t> > &transIns) {

37

IType ld. sd:

38

RType rdhwr;

unsigned long source, dest;

int sel;

41

44

45

46

source = InsP->rd;

dest = InsP->rt;

sel = (InsP->func) & 0x07;

47

48

if(source == 9){ // reading the count register of the system

transIns.push_back(rdhwr.encode(OPCODE_RDHWR,0,TEMP1,2,0,59));

51

52

53

54

transIns.push_back(sd.encode(OPCODE_SD, BASE_REG, TEMP1, (BaseGP + 8 * (dest))));

transIns.push_back(ld.encode(OPCODE_LD, BASE_REG, TEMP1, (BaseCP + (64 * source)+(8 * sel))));

transIns.push_back(sd.encode(OPCODE_SD, BASE_REG, TEMP1, (BaseGP + 8 * (dest))));

55

```

FIGURE 4: Code Snapshot of Mtc0's Translation

The first instruction will load the contents from gp source register and second will store these contents to cp destination register. The offset is created accordingly, as shown in the code. Figure 4 shows the code snapshot of mtc0's translation method.

## **2.** sll

If the instruction is: sll a1,a1,0x2. Translated instruction would be:

- 1. ld t0, offset(a7)

- 2. sll t0,t0,0x2

- 3. sd t0, offset(a7)

```

.ut 🏴 Signal Handler.cpp × 🖭 timer.h × 🖭 Processor_IPE.h × 🕾 Processor_IPE.cpp × 🖭 SystemBoard_IPE.h ×

History | 🚱 🖫 - 🗐 - | 🕄 🐶 😓 | 🔄 | 🔐 💇 | 🥚 🔲

582 → void Translation IPE::unprev R(IInfo * InsP, std::vector<uint32 t, TransInsAllocator<uint32 t> > &transIns )

void Translation IPE::shift R(IInfo * InsP, std::vector<uint32 t, TransInsAllocator<uint32 t> > &transIns ) {

RType InsX;

604

605

IType ld, sd;

606

unsigned long sourcel, dest;

607

608

source1 = InsP->rt:

609

dest = InsP->rd:

610

611

transIns.push_back(ld.encode(OPCODE_LD, BASE_REG, TEMP1, (BaseGP + 8 * (source1))));

transIns.push_back(InsX.encode(InsP->opcode, InsP->rs, TEMP1, TEMP2, InsP->sa, InsP->func));

transIns.push_back(sd.encode(OPCODE_SD, BASE_REG, TEMP2, (BaseGP + 8 * (dest))));

612

613

```

FIGURE 5: Code Snapshot Of Sll's Translation

The first instruction brings the contents from guests gp register into temporary register t0, 2<sup>nd</sup> instruction executes the actual instruction but in terms of temporary register. The third instruction stores the result of target address back to the gp register of guest. Figure 5 shows the code snapshot for sll.

## 4.3 SOFTWARE CACHE

Guest code passes through a translation layer to make it amenable to run under our hypervisor. Currently this translation is done instruction by instruction and the output is then fused together to make a block. By definition one block ends when control flow has more than one option to move forward (e.g. an unconditional jump, if-else structure etc).

Translation is a fairly involved process and it is desirable to do the translation once and re-use it on subsequent execution. There are many repetitive code structures (e.g. loops) where one block is executed more than once. To seize these performance opportunities, each translated cache is stored in a software cache. Software cache is configurable and initially set to a space for keeping 37 blocks. A class named TranslatedBlockCache is implemented which has rich set of functions to store, retrieve and search a block.

## 4.3.1 CACHE STORAGE

**Hash Map based storage:** Due to previous hypervisor architecture, translated blocks are copied at a pre-specified place where epilogue and prologue are already present along with some extra software exception handling code. To copy a block at a new location, software cache generates a new copy and stores it in the cache. Due to optimization needs, we replaced this by new array based storage. (For details see section 7)

**Array Based Storage:** Currently the translated blocks are placed in array of containers. In this method we don't copy the translated block to any particular place but instead we use the block as it is, when it is created dynamically during translation. We store a pointer to these block in a hash map for reuse.

## 4.3.2 SEARCHING A BLOCK

Software cache is capable of searching any block in time O(logn) using HashMap that is a C++ Standard Template Library (STL). Hash maps are famous for speedy searching.

Because we have changed our storing mechanism, searching has also changed. Now we find the block in array using a key and return only the pointer to that container. That's why our searching time of block has changed to O(1).

## 4.3.3 BLOCK RETRIEVAL

Software cache retrieves a block and copies it to a specified location for execution. Retrieval can be based on specific key provided at the time of storage.

Copying the block to new memory location was time consuming operation. So now, we find the presence of block in array and retrieval is done by returning a pointer to that block in array.

# 4.3.4 REPLACEMENT POLICY

A simple random replacement policy is used to replace a block when the cache is full. A block is randomly selected to replace it with the newly coming block. Replacement policy has also changed. Now, whenever a new block is required, index is generated on base of given key and old block at that index is replaced by new one. Key is converted to index using eq. Index = Key % max capacity.

For Optimization purpose, modulus operation was changed to bit shifting operation.

# 4.3.5 BUGS FIXED IN ADDRESS CACHE

- Address Cache Clearing on ASID Change: When kernel runs in user mode and starts user mode processes then multiple virtual pages can map to a single physical frame or single virtual page can be mapped to multiple physical frames. For example, for process 1 virtual address 0x120001021 can be mapped to physical address 0x41A36C021. For process 2, same virtual address (i.e. 0x120001021) can also be mapped to 0x4108D9021. To avoid conflict in address translation, address translation cache must be flushed when a process is switched. In case of process switching, kernel writes ID of new process in ASID field of EntryHi register. When ASID is changed we flush address translation cache to provide correct address translation.

- Read/Write Protection in Address Translation Cache: Guest kernel can set read/write protection of a page by setting "dirty bit" of entryLo register. When address translation is done using TLB, the state of this bit should be taken under consideration so that data may not be written to a read-only page because this can corrupt the data in RAM. Without this bit implementation memory corruption causes the guest kernel to crash during loading of dynamic libraries. Dirty bit was already implemented in TLB but was not being checked during address translation cache implementation. This implementation was provided in address translation cache for proper working of dynamic user binaries.

## 4.4 TIMER UNIT

On actual hardware, Operating system keeps track of time by receiving a timer tick after a configured time. This timer interrupt gives the timing framework to the OS above it. For

providing timer tick to guest OS, we have tried two timer infrastructures. Description of both along with their drawbacks and benefits are given.

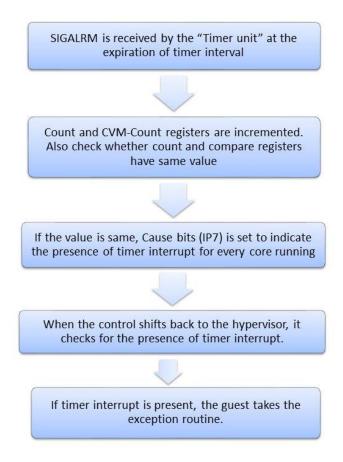

# **4.4.1** CONTINUOUS TICK TIMER

To provide the timer interrupt to the system, we have to provide a continuous tick to the guest. Timer unit is initialized in a separate thread as the hypervisor is started. The timer Unit thread registers a timer with the host OS (i.e. 5nsec interval). After every timer expiration time, the thread directly receives the SIGALRM from the host OS. On receiving SIGALRM signal, the cause register (IP7 bit) of every core is set. IP7 bit of cause indicates the presence of timer interrupt. If interrupt mask in status register is set then the interrupt would be taken after setting exception code in cause. The interrupt mask is configured by the guest itself. The cause is checked for timer interrupt every time the control is shifted to handleRequest() of hypervisor. So, timer interrupt can also be taken between the block but not necessarily at the exact time it occurred.

The timer bit (i.e. IP7) of cause is cleared, when there is a write operation on compare register. Note that this interrupt isn't handled by the CIU. CIU can only change IP2, IP3 and IP4 bit of cause register.

Implementation of Count and Cavium Count Register: Only setting IP7 in cause register, at timer expiration wasn't the correct implementation that was needed by the guest OS. Count, Compare and Cavium count registers are hardware register that are used by OS to schedule processes. Although the kernel keep the timing information by incrementing jiffies at every timer interrupt but guest also reads these hardware registers for setting timer with the hardware or getting timing information. These registers are incremented on each clock cycle by hardware and whenever value of Count register become equal to value of compare register an interrupt is generated and notifies guest about timer event which then schedules the processes and again sets time for next timer event.

In implementation, a timer is set with the host for 2ns. At timer expiration, Count and Cavium count registers are incremented and if Count becomes equal to compare register an interrupt is generated by setting the IP7 bit of cause register. Count and Compare are hardware registers and are not readable as GP or CP registers. To read hardware registers, MIPS provide

some special instruction (i.e. rdhwr). Same instruction is used to read count register. Implementation of this instruction is given to facilitate guest reading these registers and use them accordingly. Figure 6 shows the flow chart of continuous tick timer implementation in hypervisor.

**FIGURE 6: Continuous Tick Timer Implementation**

**Drawbacks:** Although this design strategy works correctly but it has two major drawbacks. First, it is computationally intense. As a periodic timer is being registered for such a short time period (i.e. 5 ns sec) and on timer expiry we have to increment the count by one. Also check the conditions to whether generate a guest interrupt or not. Second, even incrementing count after such short duration, the increment of count was very slow. At the command prompt, we see delayed response of entering the command and its execution due to or slower timer mechanism.

#### 4.4.2 ON-DEMAND TICK TIMER

This strategy is completely different from the Continuous tick timer. In this strategy rather than creating a separate thread, timer unit is embedded in each core thread. Now the timer works

serially with the core. Figure 7 shows the design difference in Continuous tick timer and Ondemand timer.

FIGURE 7: Design Diagram of Two Timer Strategies

In Continuous tick timer, a complete timer device was created. But On-Demand timer works on different strategy. Previously, the incrementing count register mechanism was way too slow. For fixing this drawback, now the host time is directly given to guest by reading host time and setting the guest's registers. When the guest needs to get time or register a timer, it read/write the count, compare and CVMcount registers.

Whenever the guest needs to get time from hardware it reads the count or CVMcount register. We intercept this read and read the host's time in nanosecond resolution and update guest's count and CVMcount registers. When guest wants to register timer with the hardware, it writes on the compare register. The write operation is also intercepted by hypervisor and it registers a timer with the host. The duration of registered timer is kernel's desired value multiplied by a multiplying factor. This multiplying factor was needed to reduce the increased timer interrupts. Otherwise kernel get stuck in servicing the timer interrupts and actual code is not given time to

be executed. After the implementation of this strategy, the prompt is showing less latency when the command is entered.

**Advantages:** This strategy is not computationally intensive as we only update the count register when the guest reads it (i.e. on-demand from guest). Now we only register the timer when guest want a timer registered with the hardware.

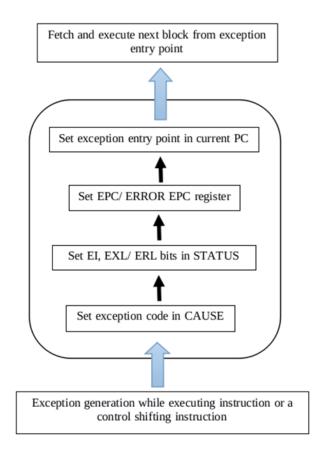

# 4.5 Interrupt and Exception Handling

Exceptions cause change in normal execution flow and control is transferred to some exception handling routines, if implemented, or crash the application otherwise. During block execution by hypervisor, two possible exceptions could occur:

- An instruction like trap or syscall, itself shifts control to an exception routine. Exceptions like these are called programmed exceptions.

- An exception like overflow, address error and tlb related exceptions are generated during the execution of instruction. This type of exceptions is unpredictable because they are not programmed.

The challenge is to emulate exception handling mechanism in user mode. On an exception, control may go to host kernel and may not return back if not emulated properly. In case of programmed exceptions, the possible emulation is to replace exception-causing instruction with innocuous instructions that explicitly transfer control back to a hypervisor provided handler. The handler could identify actual (exception-causing) instruction from control mask and handle it accordingly. In second case, a signal is raised that could be caught to handle the exception. Once the control is available in hypervisor, exception handling routine could be called to do the rest.

In our implementations, Perform\_Exception() is called to set various exception related registers. Exception code is set in cause register. EI, EXL and/or ERL bits of status register are set to indicate the presence of an exception. EPC register is set with the program counter (pc) of exception-causing instruction. According to the exception type, exception entry point is assigned to current pc so that new block could be fetched from there.

When the exception routine is completely executed, eret instruction is called. eret is privileged instruction and cannot be executed on hardware as it is (from user mode). To emulate it, we check the status register and then accordingly set pc back to the address from where exception has actually occurred. Figure 8 shows the overall flow and Figure 9 shows a snippet of hypervisor code, dealing with exception handling.

Entry point for all exceptions is generic except for tlb. For example, invalid tlb entry encountered while executing load/store instruction lead to tlb refill exception. The entry point for tlb refill exception is different from that of others. In case of nested exception (e.g. exception raised in an exception routine), general exception entry point is used and corresponding instruction pc is placed in EPC register. Interrupts are caused by external devices in order to rather communicate or in response to a request. Timer unit creates continuous interrupts in a running system for providing timing information. UART also communicate with the cores through generating interrupt.

## 4.5.1 SIGFPE: FLOATING POINT EXCEPTION HANDLING

This exception is thrown if the result of an operation is invalid or cause divide-by-zero, underflow or overflow. On production of such results during guest code execution, underlying hardware generates SIGFPE signal. Our hypervisor provide a handler to catch this signal. When control comes to this handler, we redirect it to the exception routine of guest operating system. After executing exception routine, control comes back to the handler form where it is jumped back to the immediate next instruction of exception-causing instruction.

## 4.5.2 SYSCALL: SYSTEM CALL HANDLING

The system call is the fundamental interface between user mode programs and Linux kernel. syscall() is a small library function that invokes the system call whose assembly language interface has specified number and type of arguments. Whenever the syscall instruction comes in guest code, control is transferred to hypervisor code and then redirected to corresponding exception handling routine of guest operating system. The remaining mechanism remains same as above

FIGURE 8: Exception handling in user mode

```

case HANLDE SYSCALL INT: {

printf("SysCall!\n");

Gobj->prev_PC = *blockStartPC;

Gobj->prev_PC = TLB_Exception::Perform_Exception(core0->getCP0(), HANLDE_SYSCALL_INT);

BlockManipulation::setUContext(Gobj->prev_PC,FETCH_NEXT_BLOCK);

fetchnPlaceBlock(GVA);

return true;

break;

}

case HANLDE OTHER INT: {

Gobj->prev_PC = *blockStartPC;

printf("HANLDE_OTHER_INT!\n");

P::EPRINTVAL(cntrlMark);

break;

default: {

switch(cntrlMark) {

case HANLDE_TLB_PROBE: {

if(DBG)printf("HANLDE TLB PROBE!\n");

core0->getTLB()->tlb_probe();

if(DBG)printf("Index Register = 0x%016llx\n", core0->getTLB()->get_index());

return true;

break;

```

FIGURE 9: Code snippet showing the emulation of exception handling

# 4.5.3 TLB AND ADDRESS ERROR EXCEPTION HANDLING

When the load/store instruction has to be performed in hypervisor first the address on which the load or store has to be performed, is translated into hypervisor address. During this translation, privileges are checked, whether this address is allowed to be accessed or not. If not then address error exception is generated and the next block fetched would be from the exception entry point. But if we have an address which is not violating any privileges, then the contents are looked up in TLB. If the invalid bit or dirty bit is set or no entry is present in the TLB then corresponding exception Mod, TLBL or TLBS is generated.

# 4.5.4 MODIFICATION IN EXCEPTION HANDLING

Context register was not set before in case of exception because this register is normally used in 32-bit mode but guest was using this register in user mode. Now context register is also been set so guest can read it and perform exception handling correctly.

## 4.5.5 EXTERNAL INTERRUPTS

Interrupts are caused by the external devices like timer and UART. When an interrupt occurs it set the "pendingInterrupt" variable, which indicates that external interrupt is present. Before fetching the next block, it is checked whether there is any pending interrupts or not. If they are present then some particular bits of status are checked to determine this interrupt should be passed or not. The exception code set for the interrupt is zero and routed to general exception entry point. It is the responsibility of the kernel handler to figure out what kind of interrupt has occurred and dispatch it to proper handler.

## 4.5.1 CTRL+C SIGNAL FOR GUEST

CTRL + C signal is used to terminate a process in OS. When we press CTRL+C the host OS terminates hypervisor instead of terminating process in guest. For implementing process termination in guest, hypervisor captures this termination signal and sends CTRL+C ASCII character to guest through UART. When guest kernel receives CTRL+C through UART, it terminates a guest process. CTRL+A should be pressed for terminating hypervisor.

# 4.6 SMP SUPPORT

As mentioned in our high level design, every core will be running in a separate thread that will make our hypervisor a multithreaded process. For providing SMP support, some code level structural changes were needed (e.g. removing all global variables and creating separate objects for each core). Figure 10 shows the multithreaded view of hypervisor, with cores and CIU as separate threads. First hypervisor initialize the necessary data structures and objects. Then it loads uboot binary and dork child threads according to the number of cores initialized and other parallel units. Initially only Core 0 is running and other cores are is sleep mode. After some booting process core 0 enables all other cores. This enabling and controlling mechanism is carried out through CIU (Central Interrupt Unit). The other mechanisms like fetch, translate and execution of blocks remains the same for all cores (section 4.2). Figure 11 shows the modified flow chart of hypervisor.

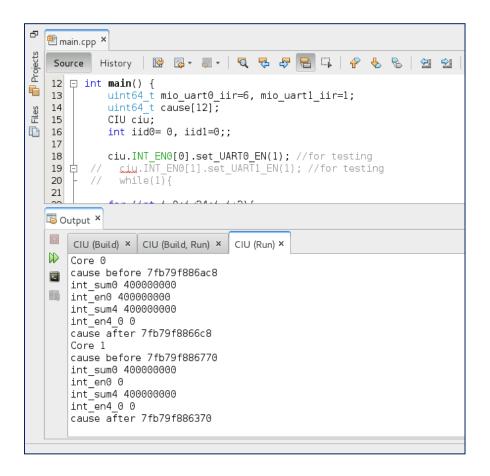

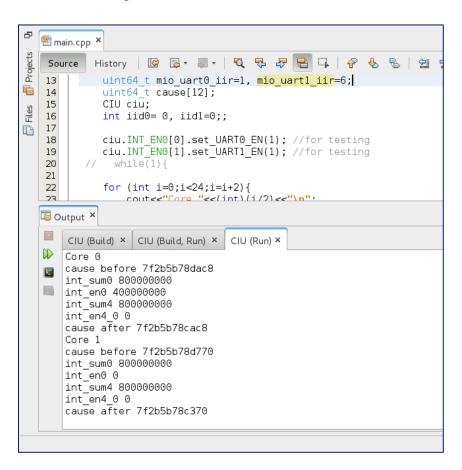

# 4.6.1 INTER-CORE COMMUNICATION THROUGH CIU

For Cavium mips64, inter-core communication is performed through CIU. Specific CIU registers (like CIU\_Fuse, CIU\_NMI, CIU\_PP\_RST and mailbox registers) are used during interrupt dispatching and identification. CIU\_Fuse register contains the information about the number of processors in the hardware. Operating system can have have this information by reading CIU\_Fuse register. After some initial booting process core 0 signals other cores to initialize themselves. To do so, primary core (i.e. core 0) sets a bit corresponding to the particular core in CIU\_PP\_RST register and that core initializes itself on low power mode.

CIU unit and other cores are all in separate threads. The threads running cores (else than primary core) will initially be in sleep mode. Core 0 sends NMI pulse to each core by setting corresponding bit in CIU\_NMI register, secondary cores goes out of low power modes and start initializing core.

FIGURE 10: Multithreaded view of hypervisor and external devices

FIGURE 11: Execution flow of hypervisor with SMP

### 4.7 IO DEVICE MANAGEMENT

In hypervisor, each core and IO device is emulated in separate thread. When a core has to communicate with any device it either reads or writes IO device register. Corresponding IO device is notified and device updates its flags according to the operation. Implementing each device in a separate thread enables maximum parallelization.

To notify IO device thread, a separate class is defined named DeviceMessageBox. It contains address which is being accessed, data which is being written to the register at specified address and whether it is read/write operation. Some posix variables are also part of DeviceMessageBox which are required for thread communication.

At time being, only 2 IO devices are implemented

- 1. UART (Universal Asynchronous Receiver Transmitter)

- 2. CIU (Central Interrupt Unit)

#### **4.7.1 UART**

The UART is typically used for serial communication with a peripheral, modem (data carrier equipment, DCE), or data set. Either a core or a remote host can use the UART. The cores transfer bytes to and receive characters from the UART core via 64-bit CSR accesses. The UART core transfers and receives the characters serially. Either polling (during booting/ in kernel mode) or interrupts (after booting/ in user space) can be used to transfer the bytes. Processor communicates with console and keyboard using UART device. So, its implementation was inevitable for a complete booting system.

There are basically 12 register in UART.

- **RBR** (Receiver Buffer Register): Receiver buffer register contains data received from input device. Whenever data is received, "Data Available" flag is set in LSR and an interrupt is generated by the UART so that processor can get received data.

- THR (Transmitter Holding Register): Transmitter holding register contains data which is being transmitted to the output device. Whenever this register is written, "THR empty" flag is cleared in LSR and UART starts transmitting data. After data is

- being transferred successfully, "THR empty" flag is set in LSR and interrupt is generated to tell the processor that UART is idle now and ready to send new data.

- **IER (Interrupt Enable Register):** Interrupts are not generated unless UART is told to do so. Processor enables UART interrupts by setting corresponding flags in Interrupt enable register.

- IIR (Interrupt Identification Register): Whenever an interrupt is occurred, processor jumps to its interrupt routine. The interrupt routine must know which kind of event caused that interrupt so that it can service it properly. IIR register tells the processor about the cause of interrupt.

- FCR (FIFO Control Register): FIFO is used in UART for both receiver buffer and transmitter buffer. Whenever data is received, it is placed in RBR. But if RBR is not empty then data is moved to receiver FIFO. When UART is transmitting data and new data is provided by processor then it is placed in transmitter FIFO. FCR is used to control the behavior of the FIFOs.

- LCR (Line Control Register): LCR is set at initialization time and controls the parameters of line. Parity and number of data bits can be changed using LCR. DLD and DLH can also be accessed by setting "DLAB" flag in this register.

- MCR (Modem Control Register): MCR register is used to perform handshaking actions with attached devices. Setting and resetting of control registers is done using this register.

- LSR (Line Status Register): LSR shows the current state of communication. Errors are reflected in this register. The state of receiver and transmitter buffers is also available.

- MSR (Modem Status Register): MSR contains information about the four incoming

modem control lines on the device. The information is split in two nibbles. The four

most significant bits contain information about the current state of the inputs where

the least significant bits are used to indicate state changes. The four LSB's are reset,

each time the register is read.

- SCR (Scratch Register): There is no use of this register in UART communication. Sometimes it may be used by processor to store a single byte.

• DLL (Divisor Latch LSB) and DLM (Divisor Latch MSB): For generating its timing information, UART uses an oscillator. Oscillator frequency is divided by 16 and obtained value is further divided by value placed in Divisor Latch registers. In this way, baud-rate of UART is adjusted. For error free communication, both receiver and transmitter UART have same timing base i.e. have same baud-rate.

**Implementation of UART:** There are basically two functions of UART. Transmit data provided by the processor and receive data from input devices. For both these functionalities we have separate threads called Receiver Thread and Transmitter thread.

- Receiver Thread: The purpose of receiver thread is to handover data to processor which

we input using keyboard. This thread continuously checks for availability of input from

keyboard. Whenever input is available, it sets "Data Available" flag in LSR and

generates an interrupt. When processor reads received data, "Data Available" flag is

cleared from LSR.

- Transmitter Thread: The purpose of transmitter thread is to transmit data which is being provided by the processor. Transmitter thread helps the processor in printing all the messages on the console. After transmitting data, it sets "THR is empty" flag in status register and generates an interrupt to tell processor that UART is free now for further transmission.

- Interrupt Generation: When UART performs an operation, it checks it IER. If interrupt for corresponding action is enabled, it sets appropriate flags in IIR and notifies the CIU thread about interrupt generation. CIU reads enable registers of all the cores to check if any core wants to receive UART interrupt. If it finds the core with enabled UART interrupt, it sets summary register for that core and generates interrupt. Core jump to its interrupt routine and service the interrupt.

#### **Modification in UART implementation:**

In previous version, some characters of guests console output were sometimes missed due to two problems. First, "printf()" was used to print characters which is in fact formatted output and takes much time so we implemented this mechanism with "write" system call which is

unformatted and is faster than "printf()". Second, wait mechanism was introduced in core implementation. Core waits for the UART to print previous characters before sending new ones.

## 4.7.2 CENTRAL INTERRUPT UNIT (CIU)

CIU is responsible for dispatching interrupt requests (coming) from external devices to a particular core. CIU is discussed here in context of our test bed i.e. Cavium Networks OCTEON Plus CN57XX evaluation board [1]. CIU distributes a total of 37 interrupts i.e. 3 per core plus 1 for PCIe. Three interrupts for each core set/unset bit 10, 11, 12 of Cause register of the core. Using these cause register bits, interrupt handler of a core could prioritize different interrupts. Interrupt requests from external devices are accumulated in a 72-bit summary vectors with naming convention CIU\_INT<core#>\_SUM<0|1|4>. Summarized interrupts reach to their ultimate destination by using corresponding 72 bits interrupt enable vector with naming convention CIU\_INT<core#>\_EN<0|1> and CIU\_INT<core#>\_EN4\_<0|1>.

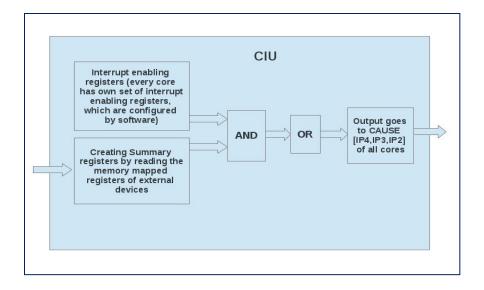

Interaction of CIU, external devices and cores is shown in figure 12 (a). CIU reads memory mapped registers of the external devices to know about pending interrupt requests and sets corresponding bits of cause register of target core. Figure 12 (b) shows a simplest description of the internal working of CIU, where interrupt identification/handling is done in software.

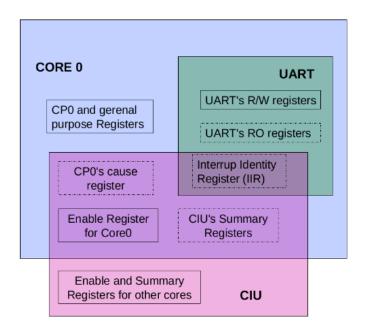

We have implemented a simplest abstraction of CIU. It has been integrated in a copy of main hypervisor code and works as a separate thread. CIU is only reading CP0's cause register. As UART is not fully developed yet, UART's memory mapped registers are artificial (for the time being). UART writing and other devices would be implemented in future. CIU itself has set of summary and enable registers for every core. An interrupt request goes to only those cores that had enabled the interrupt by configuring its enable register. In current code, CIU reads UART's Interrupt Identification Register (IIR), extracts identity bits and set/clear the corresponding summary registers bits. These summary registers for every core are than "AND" with their enable registers to set or clear cause register's bit 10, 11 and 12.

FIGURE 12(A): (CIU) Interrupt distribution from external devices to core

FIGURE 12(B): Internal working of CIU, inwards arrow comes from external devices and outward arrow goes to all cores

FIGURE 13: Memory mapping between core and external devices

In integrated code, shared memory regions are defined for CIU to work with other components of virtual board (see figure 1). Figure 13 shows these shared memory regions for core0, CIU and a single device i.e. UART. Region overlapping and dotted lines represent the accessibility and access mode of registers, respectively. For example, CP0 Cause register belongs to core0, CIU can access it but UART cannot. As Cause register belongs to core0, it can be read-written by core0 but it is read-only for CIU. IIR register of UART is read-only for CIU and Core0, hence it is at the intersection of three regions and have dotted boundary. CIU's summary registers are read-only for core0, hence dotted and at the intersection of two regions. As CIU's enable register is readable and writeable for core0 and CIU, it has solid boundary and lies in overlapped region.

## 5 Virtual Disk

A virtual disk (also known as a virtual drive or a RAM drive) is a file that represents as a physical disk drive to a guest operating system. The main idea of providing disk to guest was to create persistence of data across boot. The guest should be able to create and store files on the drive.

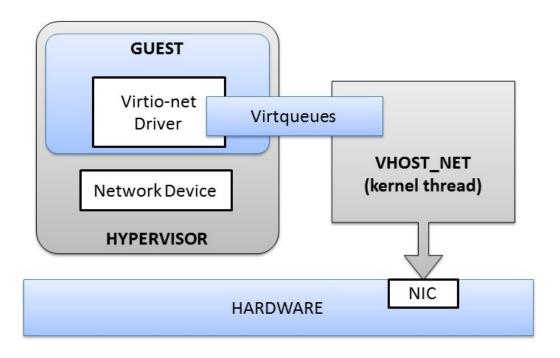

Virtio and Vhost can be configured for block devices such as Disk. Virtio para-virtualized driver for emulation of disk was used. Virtio driver directly interacts with Vhost client in host

kernel and hypervisor only works on control path i.e. notifying host kernel when data is provided by guest or sending interrupt to guest when vhost completes its assigned task. Due to some limitations, we cannot use Virtio\_Blk or Vhost\_Blk directly for this purpose and some changes have to be made.

### 5.1 VIRTIO BLOCK CONFIGURATION

In guest kernel, virtio block is already present and can be enabled from "menuconfig" of kernel. But virtio devices are implemented as PCI devices in kernel. As PCI bus hasn't been implemented in hypervisor so some changes are required in these drivers to configure them as MMIO based devices. Figure 14 shows the code that needed to be added in virtio blk.c file.

```

static struct platform_device *vblk_virtio_device;

static void register mmio device (void)

int ret;

struct resource vblk_resources[] = {

.flags = IORESOURCE MEM,

}, {

.flags = IORESOURCE IRQ,

};

vblk virtio device = platform device alloc("virtio-mmio", 0);

if(!vblk_virtio_device)

printk("***%s device struct initialization failed\n", func );

vblk resources[0].start = 0x1180070000200ull;

vblk resources[0].end = vblk resources[0].start + 0x120;

vblk resources[1].start = OCTEON IRQ GPIO0;

vblk resources[1].end = OCTEON IRQ GPIO0;

ret = platform_device_add_resources(vblk_virtio_device, vblk_resources,

ARRAY SIZE(vblk resources));

if (ret)

printk("***%s: device resource allocation failed\n", func );